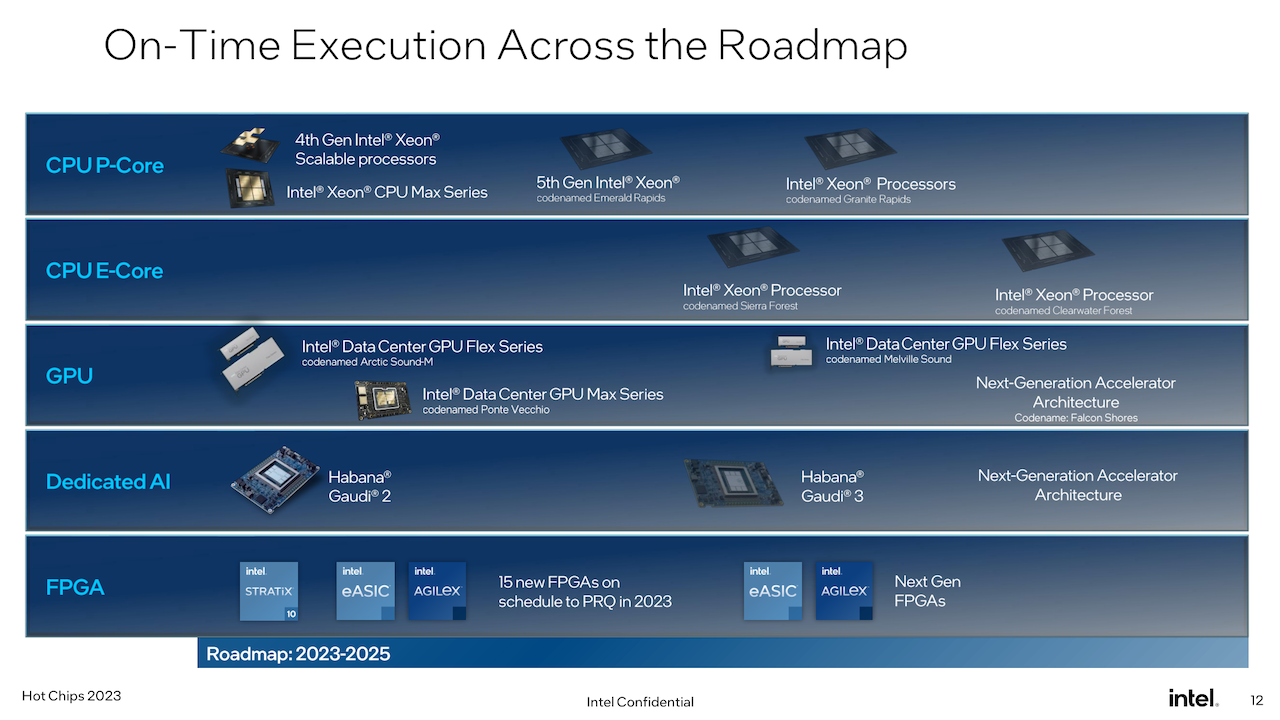

Con motivo de la feria Hot Chips 2023 (del 27 al 29 de agosto en la Universidad de Stanford), Intel destacó la quinta generación de procesadores Xeon Scalable, con nombres en código Granite Rapids y Sierra Forest, cuya comercialización se espera para 2024. La última hoja de ruta del fabricante de chips, presentada el pasado mes de marzo, ya había revelado algunos detalles técnicos sobre la arquitectura de estos chips para servidores. Granite Rapids y Sierra Forest ya se perfilan como una actualización importante en el ecosistema de servidores de Intel, gracias a la introducción de núcleos E de bajo consumo (hasta 144 núcleos por chip) y soporte para CXL 2.0. Los E-cores (bajo consumo), ya integrados en los chips convencionales de Intel desde la 12.ª generación de Core (Alder Lake), llegan al Xeon Scalable. A diferencia de los componentes de consumo donde ambos tipos de núcleos (rendimiento y bajo consumo) se mezclan en un solo chip, Intel opta por una estrategia diferente con Granite Rapids totalmente P-core y Sierra Forests equipados con E-core.

Como el primer chip Xeon Scalable E-core destinado a centros de datos (servidores únicos y bisocket para cargas de trabajo tradicionales y en la nube), Sierra Forest es posiblemente el más importante de los dos chips. Oportunamente, este es el primer Xeon grabado con tecnología Intel3 basada en EUV. Según el fundador, la entrega está prevista para la primera mitad de 2024. También grabado en Intel3, Granite Rapids (de uno a ocho sockets para cargas de trabajo exigentes e IA) le seguirá justo después. La última plataforma agrega soporte adicional para instrucciones AMX (FP16) para acelerar cierto procesamiento. Además, Intel también presentó su serie Agilex 9 Direct-RF (FPGA) con convertidores de datos integrados de 64 Gsps (gigamuestras por segundo) y un nuevo diseño de referencia que incluye receptores de banda ancha y de banda estrecha en el mismo paquete de múltiples chips. El receptor de banda ancha proporciona un ancho de banda RF de 32 GHz a la FPGA.

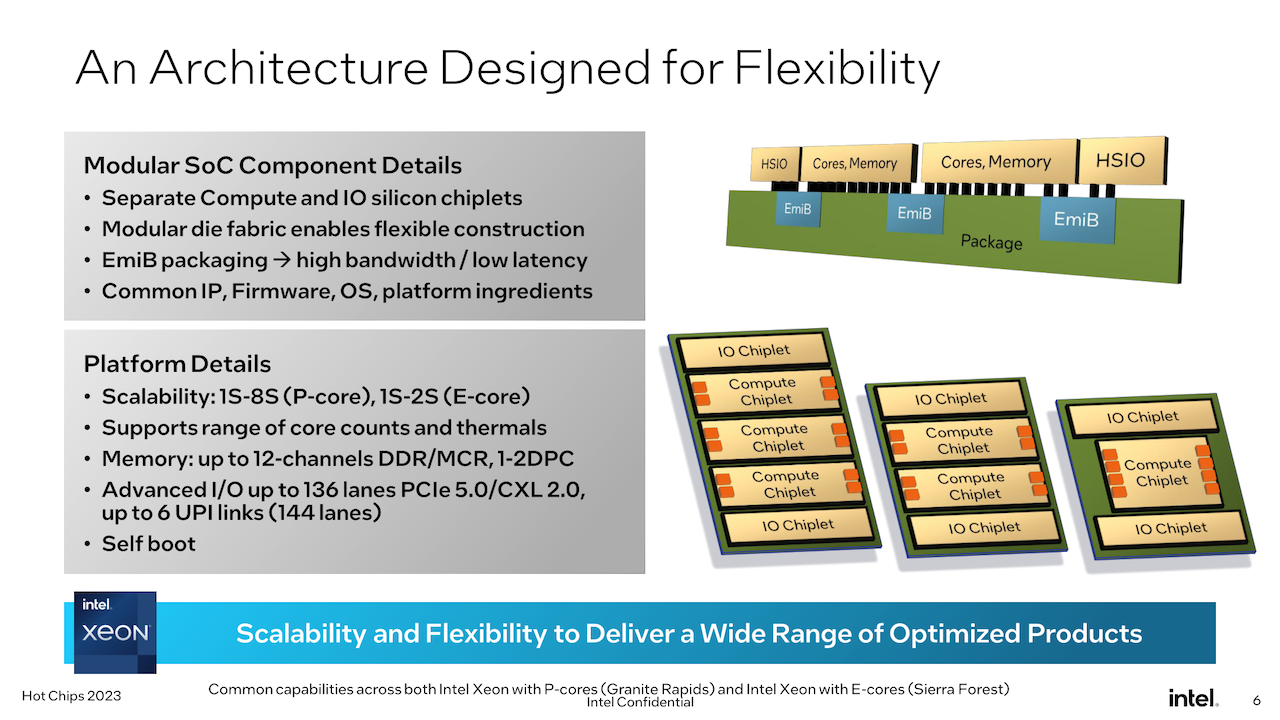

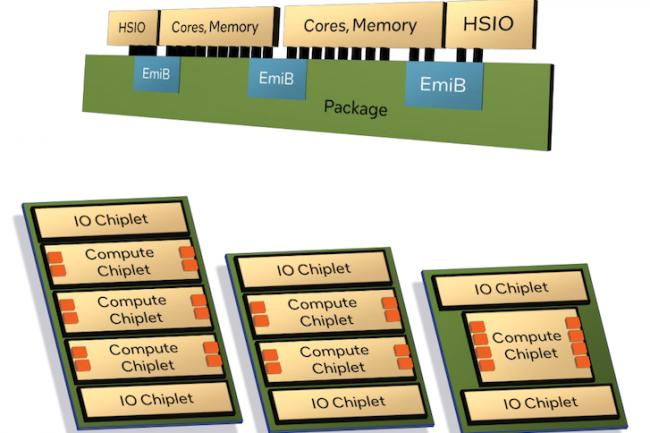

Intel está ampliando el uso de la tecnología chiplet para el diseño de sus chips Xeon con bloques modulares. (Crédito Intel)

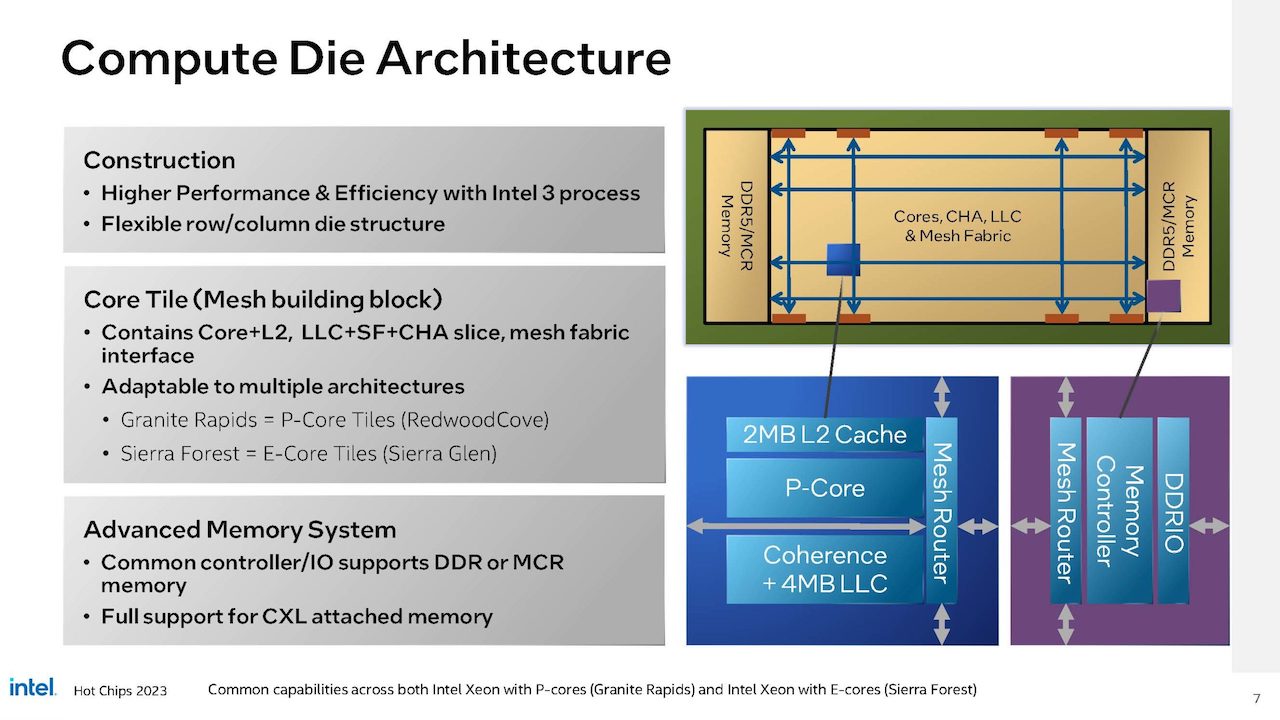

Como anunció Intel en 2022, Sierra Forrest y Granite Rapids se basan en una arquitectura de chiplet, que se basa en una combinación de bloques de computación y de E/S ensamblados mediante tecnología de puente EMIB. Esta no es la primera vez que el fundador produce Xeons en modo chiplet, ya fue el caso con Sapphire Rapids, pero es una evolución del diseño de chiplet utilizando bloques de computación y E/S. separe en lugar de ensamblar chipsets Xeon completos. Esto significa que Sierra Forrest y Granite Rapids pueden compartir un chiplet de E/S (fabricado en Intel 7) y chips de cálculo E-core o P-core (fabricados en Intel3). Para los núcleos utilizados con las series E y P, Intel reutiliza la arquitectura básica inaugurada con sus componentes de consumo. Por lo tanto, Granite Lake y Sierra Rapids pueden considerarse una CPU Meteor Lake deconstruida, con Granite obteniendo los núcleos P de Redwood Cove, mientras que Sierra obtiene los núcleos E de Crestmont, ambos debutando con la arquitectura Meteor Lake (Core 14th Gen).

Para su Xeon de quinta generación, Intel reutiliza la base de núcleos utilizados con el Core Meteor Lake. (Crédito Intel)

El fundador también confirma que esta plataforma Xeon Scalable tiene capacidades de inicio automático, lo que la convierte en un verdadero SoC. Debido a que el fundador coloca toda la funcionalidad de E/S necesaria para la operación en los chiplets de E/S, no es necesario un chipset externo (o FPGA) para operar estos procesadores. En términos de características, esto acerca la línea Xeon de Intel a la Epyc de AMD, que ha comenzado de la misma manera desde hace un tiempo. En total, esta plataforma Xeon Scalable admitirá hasta 12 canales de memoria, escalando según la cantidad y las capacidades de los núcleos presentes. Como informó anteriormente Intel, esta plataforma será la primera en admitir rangos combinados de multiplexor DIMM (MCR), que esencialmente agrupa dos conjuntos/rangos de chips de memoria para duplicar el ancho de banda efectivo hacia y desde el DIMM. Con la combinación de velocidades de bus de memoria más altas y más canales de memoria, la compañía afirma que la plataforma puede ofrecer 2,8 veces más ancho de banda que el actual Xeon Sapphire Rapids Xeon (cuarta generación).

Intel planea lanzar sus Xeon especializados en la primera mitad de 2023 (Crédito Intel).

En cuanto a E/S, una configuración Xeon máxima podrá ofrecer hasta 136 carriles de E/S, así como hasta 6 enlaces UPI (144 carriles en total) para conectividad de múltiples sockets. Para E/S, la plataforma admite PCIe 5.0 (PCIe 6.0 está en proceso), así como el protocolo CXL 2.0 para explotar recursos componibles como RAM, aceleradores, flash o red.

Otras noticias que te pueden interesar