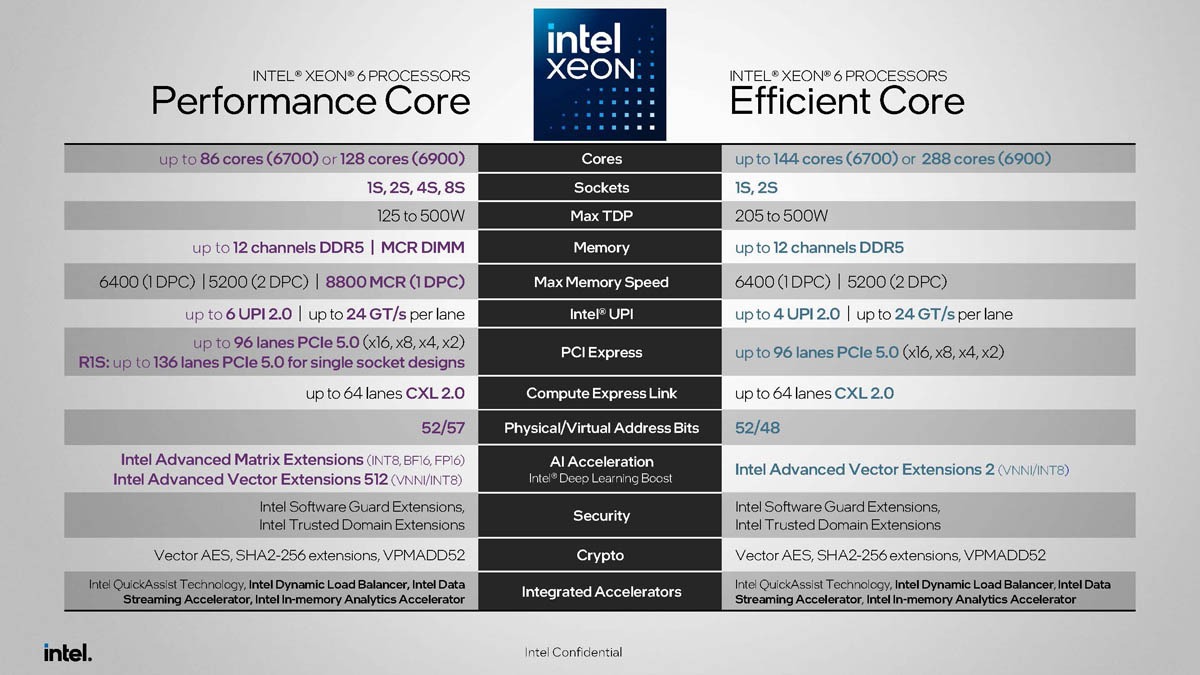

Esperada desde hace casi dos años, la renovación de la familia Intel Xeon finalmente ha comenzado. Después de los Xeon Scalable, el fabricante parece simplificar sus nombres con la introducción de los Xeon 6 Series-P (Granite Rapids) y, sobre todo, Series-E (Sierra Forest). Por primera vez en casi una década (nadie lamenta realmente el Xeon E3 y los Atom S1200 y C2000), Intel ofrece dos arquitecturas de servidor diferentes, la de los núcleos P de rendimiento (basados en los núcleos Redwood Cove) y la de los núcleos E de eficiencia (con núcleos Crestmont, ya utilizados en los Core Ultra Meteor Lake): aunque las dos plataformas comparten tecnologías básicas, el AVX-512, las instrucciones AMX (muy útiles para la aceleración de la IA) y el hyperthreading no están presentes en los núcleos E (ver diapositiva siguiente). Para la fabricación, Intel utiliza un proceso Intel3 para los tiles de cómputo (los núcleos) e Intel 7 para los tiles de E/S de sus chips Xeon 6 (P y E).

Con el Xeon 6, Intel utiliza el grabado Intel3 para los núcleos e Intel7 para el SoC. (Crédito Intel)

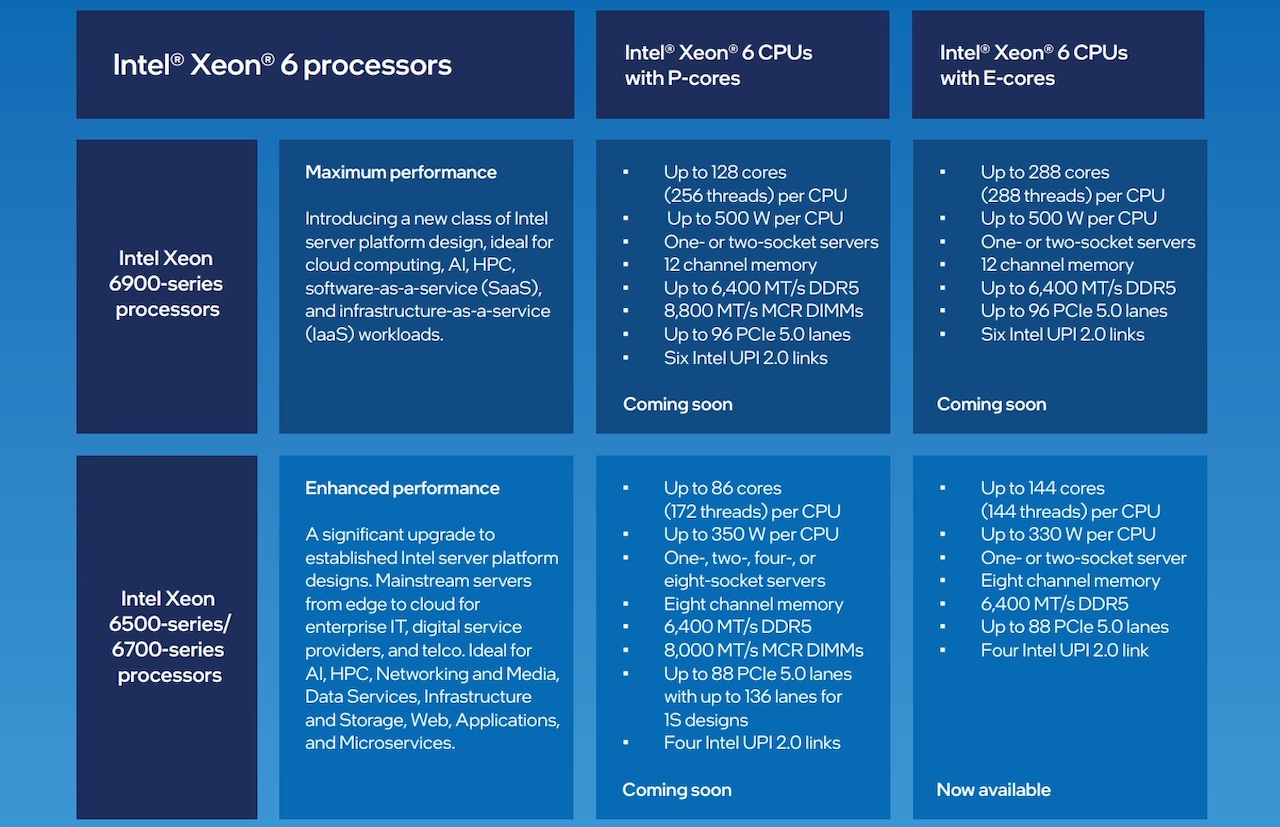

Los chips P-core fueron diseñados para ofrecer el máximo rendimiento por hilo (HPC, IA, virtualización y software licenciado en el núcleo de Microsoft y VMware) y los procesadores E-core fueron diseñados para cargas de trabajo donde la búsqueda de eficiencia energética es mayor que la del simple rendimiento con el fin de reducir los costos operativos. En instancias de nube en particular, donde las vCPU son populares entre los hiperescaladores para multiplicar instancias a un menor costo. La familia E-core - con el Xeon 6 6766E (144 núcleos Crestmont sin hyperthreading con 12 ranuras DDR5 y 96 líneas PCIe Gen5 en una envolvente TDP de 250W) - era muy esperada para poder competir con los servidores Arm, que se están multiplicando entre los hiperescaladores (Ampere, AWS Graviton, Azure Cobalt, GCP Axion y especialmente Nvidia Grace). El 6766E parece estar diseñado para competir con el Ampere Altra Max (80 a 128 núcleos Arm), que todavía está limitado a DDR4 y PCIe 4.0, y sin soporte CXL. La idea es controlar el consumo de energía de los núcleos x86, con el fin de limitar la fuga de cargas de trabajo hacia las plataformas Arm, que requieren la portabilidad de aplicaciones debido a los cambios de arquitectura. Con la serie Xeon 6 E, Intel ofrece a sus clientes la oportunidad de abandonar sus antiguos servidores x86 (Xeon Scalable de 1.ª/2.ª generación) para beneficiarse de una plataforma más moderna sin tener que recompilar sus aplicaciones que requieren un rendimiento modesto.

Intel está dividiendo el mercado de servidores en chips para IA, HPC y software facturados por núcleo, e instancias más livianas. (Crédito: Intel).

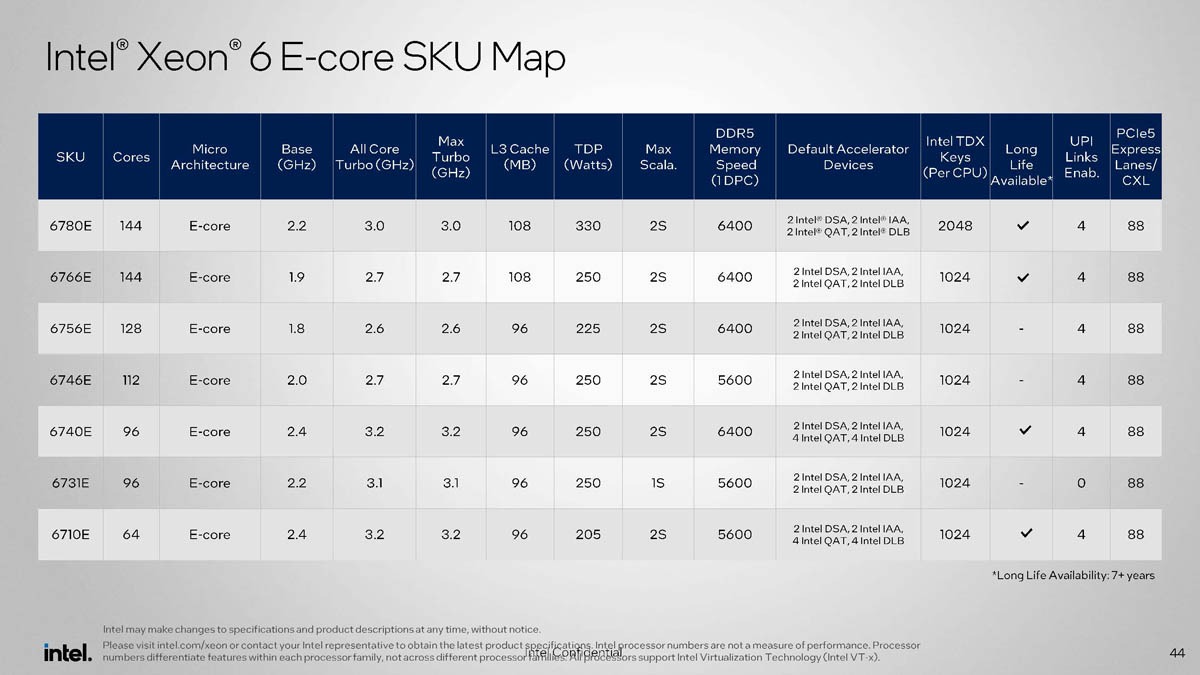

En el nivel de entrada, el Xeon 6 6710E parte de 64, 96, 112 o 128 núcleos Crestmont que funcionan a 2,4 GHz (3,2 GHz turbo en todos los núcleos). En lo más alto de la gama, encontramos el 6766E con sus 144 núcleos E y un TDP de 250 W, que funciona a una frecuencia base de 1,9 GHz (2,7 GHz turbo en todos los núcleos). Luego está el 6780E, también con 144 núcleos, pero con un TDP superior de 330 W, lo que le permite tener una frecuencia base de 2,2 GHz (3 GHz turbo en todos los núcleos). Estos dos últimos procesadores tienen 108 MB de caché L3, y el pequeño 6710E tiene 96 MB. Todos los procesadores Xeon 6 con núcleos E tienen, además, 96 líneas PCIe 5.0 y 64 líneas CXL 2.0. En modo componible, CXL permite crear pools de recursos de memoria, como Numa, Flash, GPU o sistema Ethernet a través de la interfaz PCI. Cabe destacar que en el primer trimestre de 2025, Intel presentará sockets grandes (LGA7529) con el 6900E Sierra Forest-AP con 288 núcleos y un TDP de 500W, disponible en sockets simples y duales. Los 6700E se basan en el socket LGA4710 (socket pequeño).

La base técnica es similar, pero los Xeon 6 Es carecen de instrucciones AVX-512, AMX y hypertheading. (Crédito Intel)

Con su alta densidad basada en E-Cores, el Xeon 6 6700E ofrece hasta 4,2x de aumento de rendimiento y hasta 2,6x de reducción por vatio para la transcodificación de vídeo en comparación con Xeon Scalable de segunda generación, explicó el CEO de Intel, Pat Gelsinger, durante su presentación en Computex 2024. Y la consolidación a nivel de rack es tan alta como 3 a 1, lo que reduce significativamente el espacio ocupado por racks en un centro de datos y, por lo tanto, permite más servidores. En los últimos años, Intel ha estado trabajando para mejorar el rendimiento por núcleo en sus E-cores. Estos ya no son solo núcleos más lentos, sino que están a la altura del nivel de rendimiento de un Xeon E5 V4 o un Xeon Scalable Emerald Rapids, explicó la compañía.

Los chips Xeon 6 6700E estarán disponibles en el tercer trimestre de 2024. (Crédito: Intel)

Se espera que los procesadores Intel Xeon 6 con núcleos P se lancen en el primer trimestre de 2025 y ofrecerán un rendimiento mejorado para las cargas de trabajo más exigentes, incluidas la inteligencia artificial, la computación de alto rendimiento, el procesamiento de imágenes y el análisis de datos. En la parte superior de la gama, Intel está posicionando el 6900P (zócalo grande LGA7529) con hasta 128 núcleos (Redwood Cove), 12 canales de memoria y la capacidad de usar DIMM MCR, que proporcionan un ancho de banda cercano al de los Xeon Max, pero sin la necesidad de la memoria HBM, muy cara y de menor capacidad. Este chip admite 96 líneas PCI 5.0 (hasta 136 en la versión de un solo zócalo) y 64 líneas CXL 2.0. En el nivel de entrada, encontramos el 6700P (zócalo único LGA4710) con 16, 48 u 86 núcleos P (Redwood Cove) y el mismo E/S (ver diapositiva). Nos estamos perdiendo un poco con todas estas referencias de la serie P y la serie E en diferentes sockets y disponibles en fechas lejanas: 6700E en el tercer trimestre de 2024 y 6900P, 6900E y 6700P en el primer trimestre de 2025.

Con sus dos series de chips, Intel abre el camino a su futura gama de servidores, que será más especializada y mantendrá una arquitectura totalmente compatible en el mismo ecosistema de software. La amenaza actual ya no proviene realmente de AMD, sino de los sistemas basados en la arquitectura ARM, que atrae a un gran número de hiperescaladores.

Otras noticias que te pueden interesar