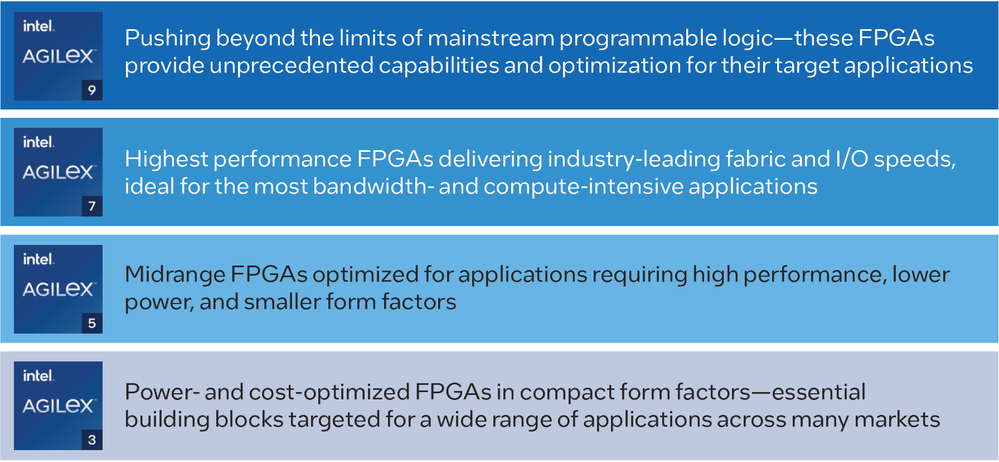

Con motivo de su evento de Innovación en San José, los días 19 y 20 de septiembre, Intel actualizó su gama FPGA con ofertas de costos optimizados, publicó su pila de software FPGA como código abierto y presentó una plataforma de procesador basada en la arquitectura RISC-V. El primero de los productos presentados es la familia Agilex 3, FPGA optimizadas en términos de rendimiento y coste, disponibles en formatos compactos. Agilex sigue la misma convención de nomenclatura de productos que los chips Core PC: 3 es el extremo más bajo del espectro de rendimiento, seguido por las series 5, 7 y 9 en orden ascendente.

La familia Agilex 3 estará compuesta por varias ramas: las series B y C. Los FPGA de la serie B tienen una mayor densidad de E/S en factores de forma más pequeños y un menor consumo de energía que otros FPGA del fundador de Santa Clara. Estos circuitos programables están destinados a la gestión de placas y sistemas, incluidas las aplicaciones de gestión de plataformas de servidores (PFM). Los FPGA de la serie C brindan funcionalidad adicional para una variedad de dispositivos lógicos programables (CPLD) complejos y aplicaciones en mercados verticales.

La familia Agilex FPGA consta de cuatro ramas. (Crédito Intel)

Intel también anunció Agilex 5 E-Series como parte de su programa Early Access, con muestras disponibles para Clientes Preferidos a partir del cuarto trimestre de 2023 y una mayor disponibilidad en el primer trimestre de 2024. Estas incorporaciones a la familia Agilex 5 están destinadas a ofrecer un mejor rendimiento por vatio que FPGA de la competencia, gracias a una mejora en el proceso de fabricación. Los FPGA Agilex 7 con R-Tile, anunciados por primera vez en mayo pasado, ya están disponibles. Según Intel, cuentan con hasta cuatro veces más ancho de banda por puerto que los FPGA de la competencia basados en PCIe 5.0 y CXL 2.0.

Pasar al código abierto

En cuanto al software, el fundador pone a disposición su software Open FPGA Stack (OFS) como código abierto. OFS está diseñado como un marco común para el desarrollo de FPGA, que ofrece bibliotecas de códigos de referencia y controladores de kernel de código abierto para Linux. OFS admite tanto Agilex como la familia de FPGA Stratix 10.

Otro anuncio se refiere al desarrollo de aceleradores IP en torno al chip Nios V, basados en la arquitectura abierta RISC-V. El Nios V/c es un microcontrolador compacto diseñado para complementar las implementaciones de FPGA. También apuntará a todos los equipos compatibles con el software de diseño de dispositivos lógicos programables Quartus Prime Pro, dijo Intel. Finalmente, el proveedor lanzó la primera unidad de procesamiento de infraestructura (IPU) F2000X (más conocida como SmartNIC). Los primeros adaptadores disponibles públicamente provendrán de Napatech, un proveedor líder de SmartNIC e IPU.

Otras noticias que te pueden interesar