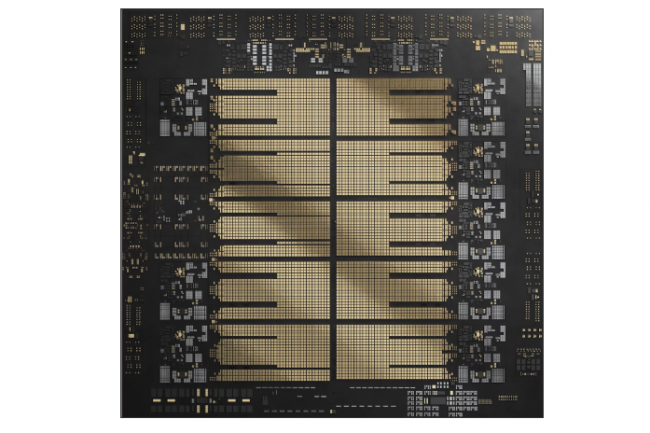

La próxima generación de mainframes z y Linuxone estará equipada con el procesador Telum 2 y un acelerador dirigido a mejorar el rendimiento de la IA y otras cargas de trabajo con alta intensidad de datos. El procesador Telum 2 tiene una mayor capacidad de memoria y caché que la generación anterior e incorpora una unidad de procesamiento de datos (DPU) especializada en la aceleración de entradas de clasificación, así como las capacidades de aceleración de la inteligencia artificial en el chip. Desarrollado con la tecnología Samsung 5 Nm, el Telum 2 tiene ocho núcleos de alto rendimiento registrados a 5.5 GHz. Incluye un aumento del 40 % en la capacidad de caché en el chip, con un cambio virtual de L3 y L4 a 360 MB y 2.88 GB respectivamente. "El poder de cálculo de cada acelerador debe multiplicarse por cuatro y alcanzar 24 mil millones de operaciones por segundo (superiores). Pero los tops por sí solos no dicen todo", escribió Christian Jacobi, desarrollo de sistemas de compañeros y CTO, y Elpida Tzortzatos, compañeros y CTO de Z/OS y AI en On On On On On On On On On On On On On On On On On On On On On On on IBM Z y Linuxone en IBM, En un blog sobre el procesador.

"Este es el diseño arquitectónico del acelerador y la optimización del ecosistema de IA que está por encima del acelerador. Cuando se trata de acelerar la IA en las cargas de trabajo de producción, la arquitectura adecuada es importante. Telum 2 está diseñado para permitir que los modelos de ejecución frotaran los hombros con las cargas de trabajo más exigentes, al tiempo que proporcionan inferencias de alta velocidad y bajas latencias". En una configuración máxima, los futuros sistemas IBM Z se pueden equipar con 32 procesadores Telum2 y 12 jaulas IO. Cada jaula puede acomodar hasta 16 ubicaciones PCIe, lo que permite que el sistema admite hasta 192 tarjetas PCIe. Los protocolos de IS/S personalizados mejorarán la disponibilidad, el control de errores y la virtualización para cumplir con los requisitos del ancho de banda masivo y garantizar la redundancia y la múltiples apasimencias para la protección contra fallas múltiples simultáneas. "También se ha integrado un nuevo cálculo primitivo para apoyar mejor los modelos de lenguaje voluminosos dentro del acelerador. Están diseñados para admitir una gama cada vez más amplia de modelos AI para un análisis completo de datos estructurados y textuales", escriben Christian Jacobi y Elpida Tzortzatos.

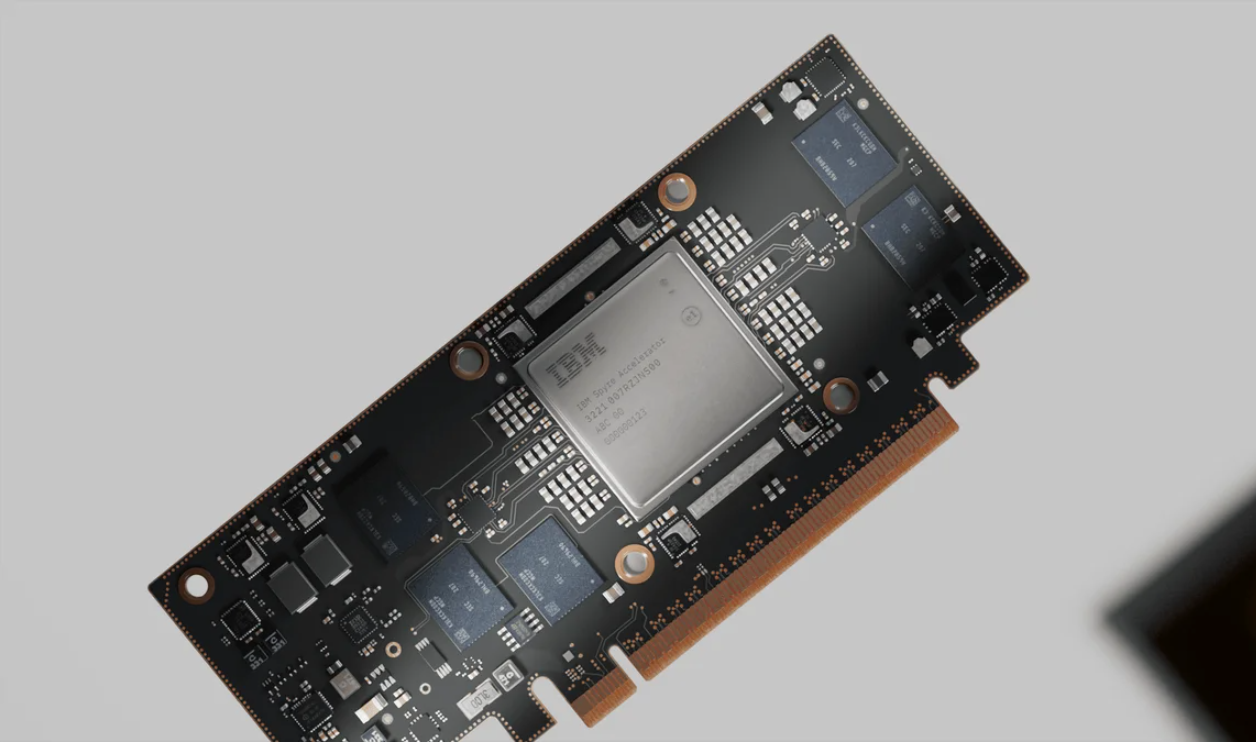

El acelerador IA Spyre tiene 32 núcleos de aceleradores individuales y contiene 25,6 mil millones de transistores. Las tarjetas se pueden agrupar; por ejemplo, un grupo de 8 tarjetas agrega 256 núcleos de aceleración adicionales a un solo sistema IBM Z.

Una DPU revisada en el chip Telum II

El primer procesador Telum de IBM, introducido en 2021, incluyó un acelerador de IA integrado para la inferencia. Con el Telum 2, Big Blue ha mejorado considerablemente la aceleración de CA, con la adición de una DPU especializada para aumentar las salidas. Según el proveedor, la DPU simplifica las operaciones del sistema y puede mejorar el rendimiento de los componentes clave. Desde el punto de vista de la red y el IS/S, una de las ventajas de este enfoque es pasar de una tarjeta de conexión de fibra óptica (FICON) a 2 puertos con una tarjeta de 4 puertos y consolidar el adaptador de sistemas abiertos (OSA) Express Ofertas, el paquete principal para la red a través de una variedad de protocolos de red, y RDMA sobre el sistema, según Michael Becht, el ingeniero principal para IBM, y los canguiños de IBM, y RDMA, y RDMA, y RDMA, y RDMA, según el sistema de Michael Becht, el ingeniero principal para IBM, y los caniculios de la red. Susan M. Eickhoff, directora de desarrollo del procesador IBM Z. "Este cambio, disponible en la próxima generación de IBM Z en la primera mitad de 2025, permitirá a los clientes mantener la misma configuración de E/O en una huella más pequeña, para reducir y modernizar su infraestructura", escribió Michael Becht y Susan Eickhoff en un blog.

IBM Spyre Acelerator

Además del procesador Telum 2, el acelerador Spyre, también grabado en 5 nm, ofrece capacidades de cálculo adicionales en términos de inteligencia artificial. En una tarjeta PCIe, el Spyre contiene 1 TB de memoria y 32 unidades de tratamiento para IA que compartirá una arquitectura similar al acelerador ACC IA integrado en el chip Telum 2, de acuerdo con Christian Jacobi y Elpida Tzortzatos: “Varios aceleradores de Spyre pueden estar conectados al subsistema IBM ZS/S a través de PCIE. La combinación de estas dos tecnologías puede ser conectado a la Mantención de la tecnología a la Mantancia a la cantidad de la tecnología de los dos años. de aceleración disponible ”. Juntos, el Telum 2 y el acelerador Spyre representan un punto de inflexión clave para Mainframe, según Steven Dickens, asesor tecnológico jefe de Futurum Group. "El hecho de que todas estas innovaciones en chips y IA provienen de IBM y se implementan en mainframes es casi lo más innovadoras e importantes posible para los clientes corporativos", dijo Dickens.

Cargas de trabajo mainframes e IA

Si bien las tecnologías de procesadores mejoran su soporte de IA y las cargas de trabajo asociadas, Big Blue tiene otras aplicaciones y usos con una alta intensidad de transacciones que también se beneficiarán de un aumento en el rendimiento y la eficiencia energética, según Tina Tarquinio, vicepresidenta de gestión de productos para IBM Z y Linuxone. "Los casos de uso de Spyre y el acelerador realmente cubren todos los casos de uso comercial que puede pensar", dijo Tarquinio. "IBM lo usa para acelerar y usar IA para ayudar a nuestras solicitudes y funciones internas de recursos humanos, por ejemplo. La próxima generación de IBM Z mantendrá su liderazgo en resiliencia, y tenemos una disponibilidad de ocho nuevos, además de ser el único sistema cuántico existente. Entornos con nubes distribuidos o híbridos. Las empresas podrán retirar las cargas de trabajo transaccionales del procesador principal y transferir estos tratamientos al acelerador para el aprendizaje automático, la IA o la evaluación y el procesamiento de la IA generativa, dijo Dickens, que es lógico desde el punto de vista operativo y evolutivo.

"Además de la generación de código, esta plataforma de IA en evolución para mainframe (chip/tarjeta/software) se adaptaría a un cierto número de aplicaciones, en particular las evaluaciones de crédito, la detección de fraude, cumplimiento, regulaciones financieras, así como el procesamiento y la simulación de documentos", dijo Patrick Moorhead, fundador, CEO y analista principal de Insumias y Estrategia Moor. "Si usted es un negocio y tiene un mainframe, probablemente lo use para aplicaciones críticas que requieren el más alto nivel de resiliencia y seguridad. Anteriormente, en el campo de la IA, las compañías trasladaron datos de la computadora central a un servidor de GPU, los procesaron y luego los devolvieron al mainframe", explica el Sr. Moorhead. “No es efectivo ni rápido y es menos seguro para solicitudes como evaluaciones de crédito, detección de fraude y cumplimiento. El Sr. Jacobi de IBM también explicó cómo la seguridad y el cumplimiento del código se beneficiarán de la nueva atención de la IA. "Muchos clientes realizan decenas de millones de líneas de código, o incluso cientos de millones de líneas de código en sus aplicaciones, y están muy preocupados por la seguridad y sensibles a la base del código", dijo Jacobi. "La base del código en sí misma es un proceso comercial codificado sobre cómo administrar una compañía de seguros o un banco. Por lo tanto, es, por supuesto, una propiedad intelectual muy preciosa para ellos.“ Cuando los clientes tienen este tipo de estructuras de código, prefieren hacerlo directamente en el entorno seguro de la computadora central, en lugar de llevar a cabo este análisis en otro lugar. Esto ahora es posible ”, dijo Jacobi.

En 2025 en el siguiente mainframes

"Con el Spyre, podemos agrupar hasta ocho tarjetas para obtener el tamaño de la memoria y la capacidad de cálculo necesaria para ejecutar cargas de trabajo de Genai en este código. Y lo integraremos en nuestros productos de nivel superior como el código de asistente de Watson para Z con modelos optimizados que están capacitados y asesinados para tener el conocimiento necesario para hacer una especie de refactor de código de mainrame y el código de código principal", dijo Jacobi. El Telum 2 será el procesador central de las plataformas de la próxima generación Z y Linuxone esperadas en 2025, según IBM. El acelerador Spyre, actualmente en una vista previa técnica, también debe estar disponible en 2025.

Otras noticias que te pueden interesar