Con UCIe, un consorcio desarrolla la interconexión de los próximos chips

hace 3 años

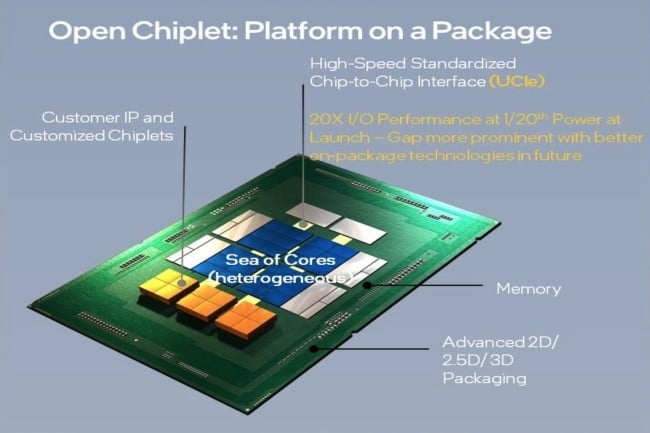

Varias empresas como Intel, AMD, Qualcomm,... están trabajando en la creación de un estándar de interconexión entre chiplets. Nombrado UCIe, allana el camino para una mayor apertura y modularidad en futuros chips.

Si en el mundo del PC siempre ha existido la modularidad, en el de los chips es más complicado. Pero ha llegado el momento de abrirse, como demuestra la creación de un consorcio que reúne a varias empresas, entre ellas Intel, ARM, Advanced Semiconductor Engineering (ASE), AMD, Qualcomm, Google Cloud, Meta, Microsoft, Samsung y TSMC (pero sin Nvidia y Apple). Este grupo trabajará en un estándar llamado Universal Chiplet Interconnect Express, o UCIe.

Este último utiliza el concepto de chiplet que tiene como objetivo combinar e interconectar diferentes módulos con su propia matriz dentro del chip y de diferentes proveedores. AMD e Intel llevan años aplicándolo: Intel con sus conexiones co-EMIB y ODI, por ejemplo, detrás del chip híbrido Alder Lake. Una asociación de ingeniería especializada entre AMD e Intel también dio como resultado un chip Intel llamado Kaby Lake G, que incorpora una GPU AMD.

Una interconexión estandarizada

El consorcio tiene como objetivo "estandarizar las interconexiones de matriz a matriz" que no existen en la actualidad. En términos concretos, la UCIe transfiere datos utilizando la interfaz PCI Express o CXL (Compute Express Link) existente que se usa en los centros de datos. De hecho, un proveedor de chips podría tomar el núcleo de la CPU de una empresa, el núcleo de gráficos de otra y el módem WiFi o 5G de una tercera, y unirlos como bloques LEGO usando UCIe. para interconectarlos. Un poco como insertar una tarjeta gráfica o un SSD en la ranura PCI Express de una PC. Pero con UCIe, la integración sería simplemente a nivel de chip. Ya está disponible un primer borrador de la norma en su versión 1.0.

El siguiente estándar es también una especie de reconocimiento: que las demandas de los diseños actuales simplemente superan la capacidad de la industria para fabricarlos físicamente. Durante décadas, la industria ha tratado de diseñar procesadores de PC todo en uno que combinen CPU, GPU, E/S y más, todo en un solo chip. Pero cuanto mayor sea el tamaño de los chips, mayores serán las posibilidades de errores de grabado, con el riesgo de inutilizar todo el componente, lo que representa una pérdida de valor para el fabricante y el diseñador.

Cada vez más chips modulares

De hecho, uno de los objetivos de la UCIe es prepararse para el día en que los próximos chips híbridos sean demasiado grandes para fabricarse con los equipos litográficos actuales. "Sería más fácil para toda la industria construir chips más pequeños y unirlos para que se comporten como una sola entidad", dijo a HPCWire Debendra Das Sharma, presidente de HPCWire. la UCIe e investigador principal de Intel.

En teoría, UCIe significaría que cualquier persona con las licencias y la propiedad intelectual adecuadas podría ensamblar chips que contuvieran los módulos de diferentes proveedores. UCIe también sugiere que las nuevas empresas podrían desarrollar chips especializados basados en UCIe y venderlos a otros especialistas en semiconductores. En verdad, esta industria ha tenido esta capacidad durante mucho tiempo con FPGA de empresas como Altera y Xilinx, ambas adquiridas recientemente por Intel y AMD.

Si quieres conocer otros artículos parecidos a Con UCIe, un consorcio desarrolla la interconexión de los próximos chips puedes visitar la categoría Otros.

Otras noticias que te pueden interesar