Con su acelerador de GPU Rialto Bridge, Intel planea alcanzar a Nvidia

hace 3 años

Con un mercado de HPC en expansión para cubrir todas las necesidades de cómputo, IA y otras, los proveedores están compitiendo para ofrecer aceleradores de GPU utilizando arquitecturas innovadoras. Mientras espera Falcon Shores, Intel está preparando el Puente de Rialto, para suceder al Ponte Vecchio.

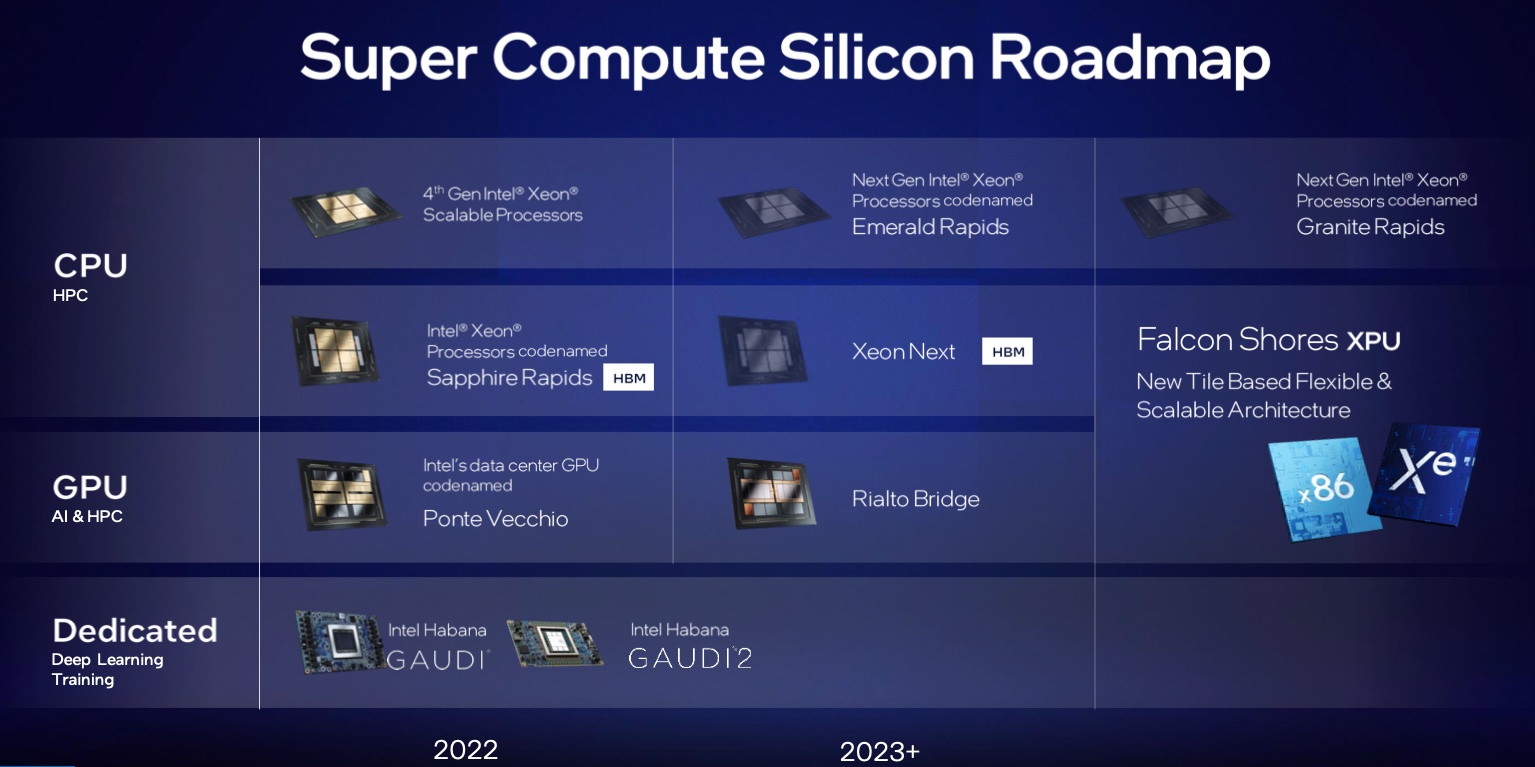

En la feria comercial ISC High Performance 2022, del 29 de mayo al 2 de junio en Hamburgo, Alemania, Intel destacó al sucesor de su acelerador de GPU Ponte Vecchio, que el fundador llamó Rialto Bridge. Esperado para 2023, hasta ahora se conocía simplemente como "Ponte Vecchio Next" en la hoja de ruta del proveedor (ver más abajo). La hoja de ruta más reciente de Intel, que abarca aproximadamente tres años, también anuncia una convergencia entre CPU y aceleradores con la plataforma XPU desagregada, de la cual Falcon Shores será el primer descendiente. Beneficiándose de las últimas tecnologías de Intel y un grabado más fino, Rialto Bridge tiene la abrumadora tarea de proporcionar un puente entre Ponte Vecchio y Falcon Shores.

La hoja de ruta de tres vías de Intel para sus CPU y GPU de clase empresarial. (Crédito Intel)

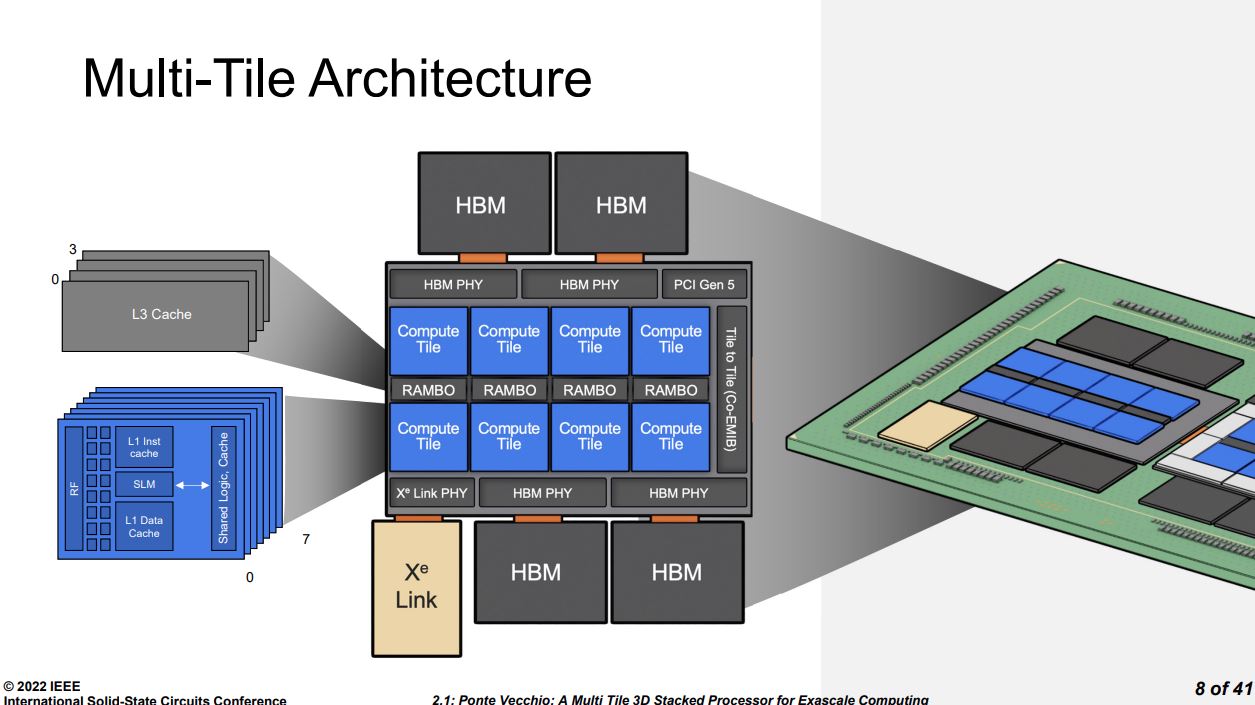

Cambio principal, el número de unidades de cálculo Xe pasa de 128 en el Ponte Vecchio a 160 en el Puente de Rialto. Para la fabricación, este último utilizará tecnologías de grabación más nuevas que la combinación actual que combina nodos TSMC N7 (para mosaicos de cómputo), TSMC N5 (para mosaicos Xe Link) e Intel7 (para base y caché). . Este último debería, por ejemplo, ser reemplazado por un proceso Intel4 para la base y el caché del acelerador. Rialto Bridge también tiene una diferencia notable con su predecesor: las unidades de cómputo se benefician de una arquitectura reelaborada, ofreciendo hasta un 30% más de rendimiento en las aplicaciones según Intel. Este último, sin embargo, aún no ha proporcionado ninguna referencia para respaldar estas declaraciones. Sin embargo, la cifra del 30 % sigue de cerca el aumento del 25 % en el número de unidades de cómputo.

160 unidades de cómputo

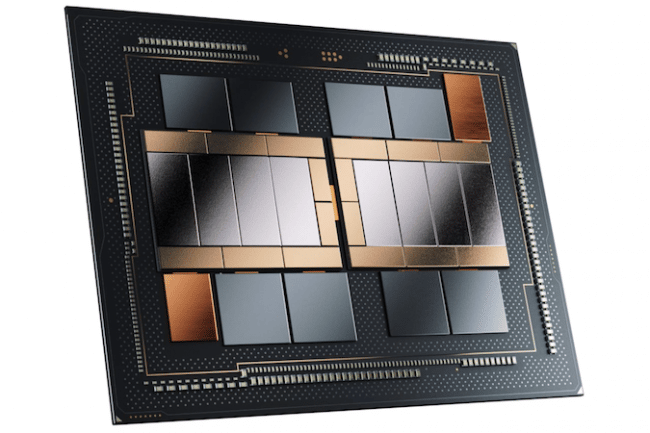

Como se muestra en la siguiente diapositiva, a diferencia del Ponte Vecchio que tiene 16 mosaicos de cómputo dispuestos en dos tiras en el centro del chip, Bridge Rialto opera ocho mosaicos con 20 unidades Xe cada uno. También se han eliminado los mosaicos de Ponte Vecchio Rambo Cache, aunque todavía quedan ocho mosaicos de HBM y dos mosaicos de Xe Link. Para el consumo máximo de energía de su próximo acelerador, Intel anuncia 800 watts, contra 600 watts para Ponte Vecchio, aún con un factor de forma Open Accelerator Module (OAM). Sin embargo, la fundición tiene la intención de pasar a la siguiente especificación OAM 2.0, aunque también continúa ofreciendo sus GPU en otros factores de forma. Para disipar este exceso de calor, el fundador confía en la refrigeración líquida e incluso en la inmersión, a pesar de las reticencias de muchos CIO por esta última.

Intel ha revisado la organización de los mosaicos de su GPU Rialto Bridge. (Crédito Intel)

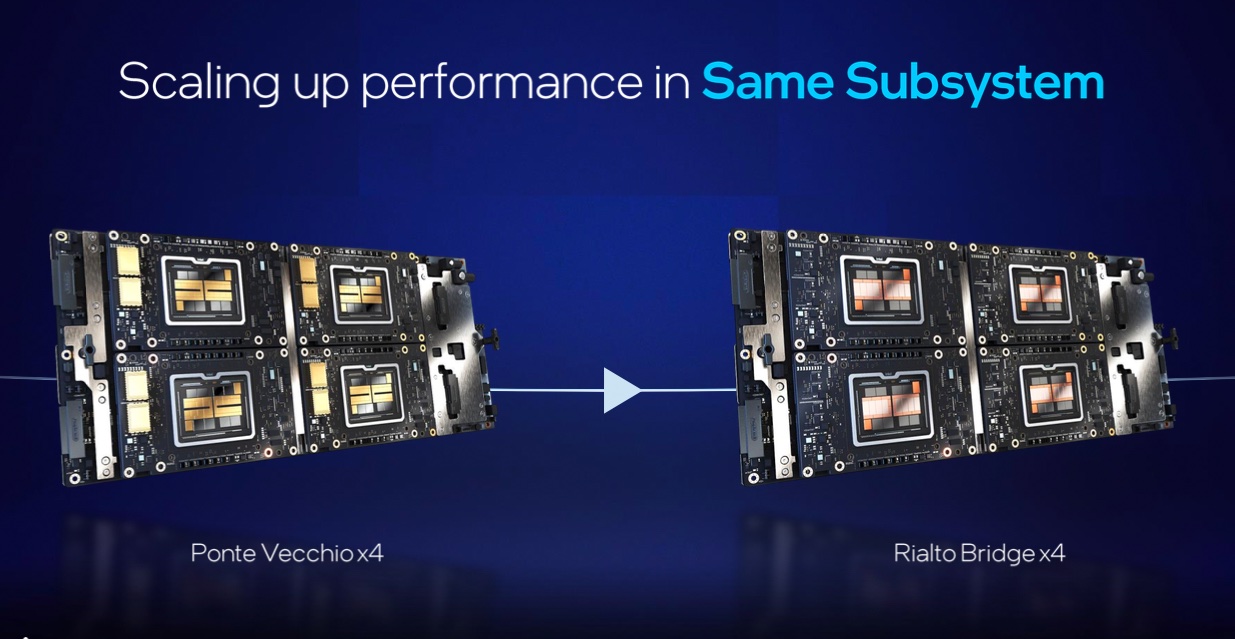

En una diapositiva, Intel también indica que el ancho de banda y la entrada/salida de sus aceleradores Rialto Bridge está en aumento sin, sin embargo, proporcionar una cifra precisa. Explotar la interfaz PCIe 5.0 con la interconexión Xe Link y, quizás, la memoria HBM3 como en el acelerador Ampere de Nvidia no es ajeno a esta afirmación. Según la hoja de ruta de Intel, las primeras copias -para muestras- del Puente de Rialto se esperan para mediados de 2023.

Las GPU Rialto Bridge vienen en el mismo empaque que Ponte Vecchio. (Crédito Intel)

Arquitectura desagregada

El otro gran anuncio de Intel en ISC es, por supuesto, Falcon Shores, previsto para 2024, que anuncia la llegada de chips desagregados con mosaicos separados de alto rendimiento para núcleos x86 y núcleos de GPU. Para crear componentes según sea necesario de CPU, GPU o una combinación de los dos para cumplir con cargas de trabajo específicas, especialmente en entornos AI/ML. Estas tejas se fabricarán con un proceso tipo Angstrom, sin más indicaciones. El objetivo final de Intel es aumentar el rendimiento por vatio, la densidad informática en un socket x86, la capacidad de memoria y el ancho de banda 5 veces en comparación con los chips de servidor existentes. Para facilitar las cosas a los desarrolladores, Falcon Shores se beneficiará de un modelo de programación simplificado que, según Intel, creará una experiencia de programación "similar a una CPU", presumiblemente basada en la cartera OneAPI del proveedor.

La plataforma Falcon Shores enfatiza CPU (x86), GPU (Xe) o una combinación de ambas arquitecturas. (Crédito Intel)

Si quieres conocer otros artículos parecidos a Con su acelerador de GPU Rialto Bridge, Intel planea alcanzar a Nvidia puedes visitar la categoría Otros.

Otras noticias que te pueden interesar